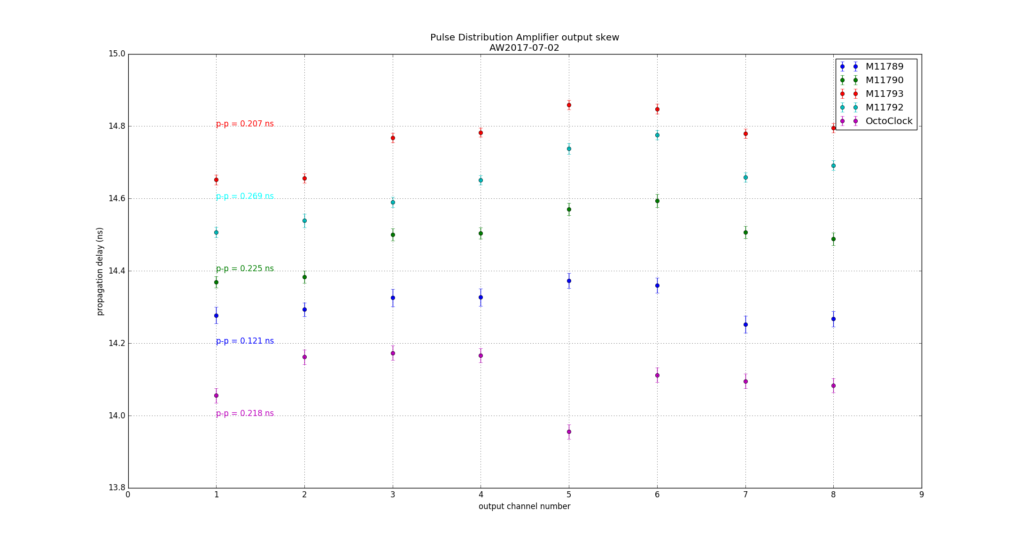

Here is the measured output delay skew from four of my "PDA 2017.01" designs, based on LT1711 comparator driving a 74AC14 schmidt trigger which in turn drives eight 74AC04 output-stages.

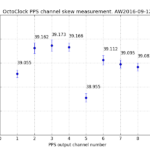

Also included is my earlier measurement of an Ettus OctoClock.

Although the PCB was designed with equal-length traces for the output stages it appears that channels 3-4 and 5-6 are consistently late, and some shortening of the traces would improve things. I tried this on one PCB (blue data points) with moderate success.

Measurement setup: 1PPS source to 50-ohm splitter. One output of the splitter drives CH1(start) of a time interval counter (HPAK 53230A), the other output drives the input of the pulse distribution amplifier. Outputs wired to CH2(stop) of the counter and measured for 100 s or more (delay is average of 100 pulses). Counter inputs DC-coupled, 50 Ohms, trigger level 1.0 V.